Photo from wikipedia

Transistor sizing is one of the most critical parts of comparator design which has a significant influence on comparator specifications. This paper presents an optimum design of a double-tail latch… Click to show full abstract

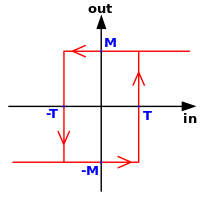

Transistor sizing is one of the most critical parts of comparator design which has a significant influence on comparator specifications. This paper presents an optimum design of a double-tail latch comparator based on transistor sizing with a great certainty to reach the best possible design due to using Hspice (as a software simulator) linked with a heuristic algorithm. To achieve a low-power, high-speed, low offset and, small size comparator, the multi-objective inclined planes optimization and Hspice were linked and several Pareto-fronts were obtained. As a result of analyzing the Pareto-fronts, power and total sizes of transistors have a tradeoff with delay and offset voltage. Meanwhile, the results comparison with a recent work shows the superiority of the present approach performance.

Journal Title: Analog Integrated Circuits and Signal Processing

Year Published: 2017

Link to full text (if available)

Share on Social Media: Sign Up to like & get

recommendations!