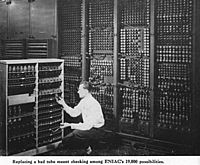

Photo from wikipedia

This work investigates the novel device structure, silicon-on-nothing electrostatically doped junctionless tunnel field effect transistor (SON-ED-JLTFET) with high-K stacked hetero-gate technology for its short channel effects (SCEs) immune properties. Here,… Click to show full abstract

This work investigates the novel device structure, silicon-on-nothing electrostatically doped junctionless tunnel field effect transistor (SON-ED-JLTFET) with high-K stacked hetero-gate technology for its short channel effects (SCEs) immune properties. Here, its analog/RF device performance metrices are also analyzed using calibrated 2-D technology computer-aided design (TCAD) simulation study. This device is expected to exhibit the fundamental advantages of SON technology, i.e. it should be more immune towards SCEs, like threshold voltage roll-off, drain induced barrier lowering (DIBL) even for devices with less than 10 nm channel length. Moreover, owing to its electrostatic doping instead of metallurgical doping, the detrimental doping control issues, such as mobility degradation, higher fabrication thermal budget and statistical random dopant fluctuations (RDFs) can no more degrade the device performance. This helps in realization of more process variations immune design. Here the detailed device sensitivity analysis with respect to the various crucial devices dimensional parameters variation is also carried out.

Journal Title: Silicon

Year Published: 2020

Link to full text (if available)

Share on Social Media: Sign Up to like & get

recommendations!