Photo from wikipedia

A 40 Gbps 4-tap 4-level pulse amplitude modulation closed-loop decision feedback equaliser (DFE) is proposed. The DFE adopts a novel high-speed comparator to resolve the critical timing constraints of the… Click to show full abstract

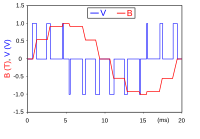

A 40 Gbps 4-tap 4-level pulse amplitude modulation closed-loop decision feedback equaliser (DFE) is proposed. The DFE adopts a novel high-speed comparator to resolve the critical timing constraints of the first tap. The comparator decreases the slicing delay by shortening the gap between initial and target voltages. Compared with the existing closed-loop DFE designs, the proposed scheme relieves timing constraints without complex clock distribution circuits and extra area. Simulations based on the RF-MOS model verify that the delay of the comparator is improved by 32.8% and the output swing is increased by more than 2.8 times. The proposed DFE which can compensate −9.5 dB channel loss is designed in 55 nm CMOS technology. The power consumption is 67 mW from a 1.2 V supply and the circuit occupies an active area of 0.021 mm2, achieving 1.68 pJ/bit energy efficiency.

Journal Title: Electronics Letters

Year Published: 2018

Link to full text (if available)

Share on Social Media: Sign Up to like & get

recommendations!