Photo from wikipedia

In this paper, a shift register (SR) memory based on rapid single flux quantum (RSFQ) logic for bit-parallel access is proposed. The memory cell changes from a row in the… Click to show full abstract

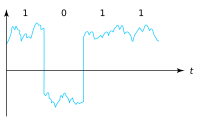

In this paper, a shift register (SR) memory based on rapid single flux quantum (RSFQ) logic for bit-parallel access is proposed. The memory cell changes from a row in the memory array to a column to increase the bit of data accessed per one clock cycle. The design of the 8 bit × 2 bit (8 × 2) memory is introduced. The memory consists of four parts: a SR memory array, an input buffer, an output buffer, and a controller, in which the controller is used to produce a control signal at a certain clock cycle specified by the address data. We have obtained the low speed test of the 8 × 2 memory fabricated by 6 kA cm−2 Nb process (SIMIT-Nb03), all bit-parallel access operations (write, read, clear and write, and read again) have been verified. We also simulated the 8 × 8 memory with data width expansion and obtained the maximum operating frequency of 34 GHz after the place and route with the SIMIT-Nb03 cell library. Based on the hierarchical storage, we have used the 8 × 8 memory as a basic block to construct large size of memory system, the access time and bandwidth have been evaluated. The bit-parallel memory shows higher bandwidth than bit-serial memory with the same capacity, especially for large capacity memory.

Journal Title: Superconductor Science and Technology

Year Published: 2021

Link to full text (if available)

Share on Social Media: Sign Up to like & get

recommendations!