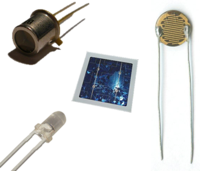

Photo from wikipedia

This paper proposes a triple-mode discrete-time incremental analog-to-digital converter (IADC) employing successive approximation register (SAR)-based zooming and extended counting (EC) schemes to achieve programmable trade-off capability of resolution and power… Click to show full abstract

This paper proposes a triple-mode discrete-time incremental analog-to-digital converter (IADC) employing successive approximation register (SAR)-based zooming and extended counting (EC) schemes to achieve programmable trade-off capability of resolution and power consumption in various smart sensor applications. It mainly consists of an incremental delta–sigma modulator and the proposed SAR-EC sub-ADC for alternate operation of the coarse SAR conversion and EC. They can be reconfigured to operate separately depending on the application requirements. The SAR-based zooming structure allows the IADC to have better linearity and resolution, and additional activation of the EC function gives the further resolution. During this reconfigurable conversion process, pipelined reusing operation of sub-blocks reduces the silicon area and the number of cycles for target resolutions. A prototype ADC is fabricated in a 180-nm CMOS process, and its triple-mode operation of high-resolution, medium-resolution, and low-power is experimentally verified to achieve 116.1-, 109.4-, and 73.3-dB dynamic ranges, consuming 1.60, 1.26, and 0.39 mW, respectively.

Journal Title: IEEE Access

Year Published: 2019

Link to full text (if available)

Share on Social Media: Sign Up to like & get

recommendations!