Photo from academic.microsoft.com

A 16-bit bit-slice arithmetic logic unit (ALU) is proposed for 32-/64-bit rapid single-flux-quantum microprocessors. It is based on a Ladner–Fischer adder. The ALU covers all of the ALU operations for… Click to show full abstract

A 16-bit bit-slice arithmetic logic unit (ALU) is proposed for 32-/64-bit rapid single-flux-quantum microprocessors. It is based on a Ladner–Fischer adder. The ALU covers all of the ALU operations for MIPS32 instructions set. And each of the two 64-bit operands is divided into four slices of 16 bits each. The ALU uses synchronous concurrent-flow clocking and consists of 11 pipeline stages. The proposed ALU can be used for any 16 n-bit processing.

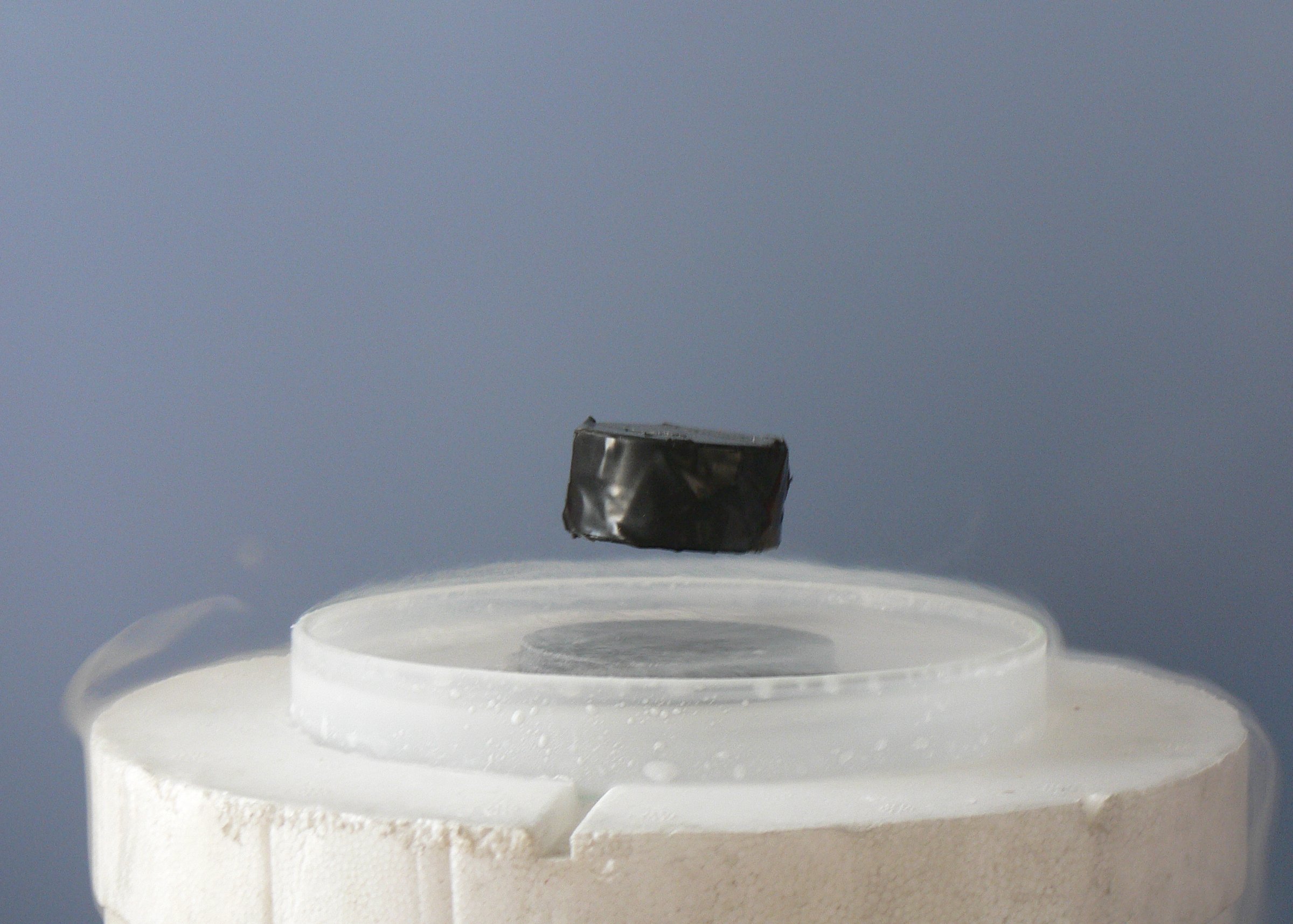

Journal Title: IEEE Transactions on Applied Superconductivity

Year Published: 2018

Link to full text (if available)

Share on Social Media: Sign Up to like & get

recommendations!