Photo from wikipedia

In this study, a novel method for the detection of recycled field-programmable gate arrays (FPGAs) is proposed. This method is based on with-in die (WID) process variation model over an… Click to show full abstract

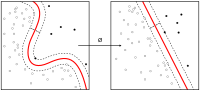

In this study, a novel method for the detection of recycled field-programmable gate arrays (FPGAs) is proposed. This method is based on with-in die (WID) process variation model over an exhaustive path characterization [referred to as exhaustive-fingerprint (X-FP)]. In the proposed method, X-FP is capable of fully characterizing frequencies on all paths in look-up tables (LUTs) using advanced ring oscillator (RO) design to exhaustively capture deterioration by aging. Although machine learning (ML)-based classification is often used for recycled FPGA detection, X-FP yields a large amount of measurement data, which cannot be appropriately handled by typical ML algorithms, if they are used as a feature vector. The proposed method utilizes the model parameters extracted by WID variation modeling as the feature vector in the ML algorithm. These model parameters simply and accurately represent the process variation for each FPGA. In this way, the ML-based fresh/recycled classification works very well with the simple feature vector. Experiments using 50 commercially available FPGAs reveal that X-FP can capture the degradation effects, which cannot be detected by conventional methods. Moreover, the WID modeling achieves 99.6% feature size reduction per one FPGA. It also demonstrates that the model parameters exhibit good distance properties between fresh and aged FPGAs. Additionally, the ML-based classification which uses a one-class support vector machine can successfully detect 2 aged FPGAs (48 h accelerated aging) without any misclassification and another 4 aged FPGAs (24 h accelerated aging) with a very few misclassifications as fresh FPGAs.

Journal Title: IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems

Year Published: 2021

Link to full text (if available)

Share on Social Media: Sign Up to like & get

recommendations!