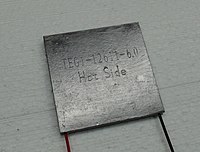

Photo from wikipedia

With the increasing demand for thermal management for high-power electronics devices and modules, a variety of double-sided cooling (DSC) encapsulation modes have emerged. In this article, we focused on the… Click to show full abstract

With the increasing demand for thermal management for high-power electronics devices and modules, a variety of double-sided cooling (DSC) encapsulation modes have emerged. In this article, we focused on the planner packaging structure and solder bump interconnection applied in DSC power modules, thermal management, and thermomechanical reliability were compared based on finite-element method under different power losses, temperatures, and temperature cycling. Results show that planner structure with copper buffer has lower junction temperature versus solder bump interconnection and lower thermal stress of the module is generated. However, chip stress of the planner packaging is high, especially under the same temperature. The planner stretches caused by normal stress is the major factor that affects the thermal stress of chip. With underfilling, reliability of solder bump is improved due to a lower plastic strain and plastic work yet simultaneous increased thermal stress. This study should advance the package of DSC modules.

Journal Title: IEEE Transactions on Components, Packaging and Manufacturing Technology

Year Published: 2021

Link to full text (if available)

Share on Social Media: Sign Up to like & get

recommendations!