Photo from wikipedia

A formal modeling of a Network-on-Chip (NoC) using a communicating finite state machine (CFSM) is presented in this article. We have automated the CFSM model generation for NoCs with Mesh… Click to show full abstract

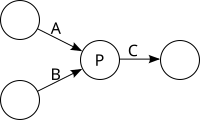

A formal modeling of a Network-on-Chip (NoC) using a communicating finite state machine (CFSM) is presented in this article. We have automated the CFSM model generation for NoCs with Mesh and Torus topologies. To verify deadlock in an NoC, we need to consider the formal model of all the routers in a given topology. It is not supported by the available verification tools due to the state space explosion problem. An NoC simulator gives only a warning message about a possible deadlock, which does not guarantee a real deadlock situation. Therefore, we have developed a simulation framework based on our CFSM models of NoCs in which any routing algorithm can be simulated over a given traffic pattern. Our simulation framework confirms real deadlock when simulation reaches a state from which no progress is possible. We have shown that this situation actually depicts cyclic dependencies among the different NoC components. As a proof of concept, we have implemented our simulation framework for one static routing and two adaptive routing algorithms. The experimental results show that our method is scalable. This is possible because we only check the existence of a deadlock for a given traffic pattern at a time, rather than for all possible traffic patterns. Our approach opens up a way to verify other NoC properties such as starvation, livelock, and so on for a given routing algorithm for any realistic traffic patterns.

Journal Title: IEEE Transactions on Very Large Scale Integration (VLSI) Systems

Year Published: 2020

Link to full text (if available)

Share on Social Media: Sign Up to like & get

recommendations!